跑馬燈

實驗室介紹

高密度光電積體電路的研發近年來成為廣受注目的研究課題,此發展將有助於延伸光路傳輸距離縮小至厘米或微米等級,藉由光電積體電路的開發整合各式主被動光電元件於單一晶片上,可以降低各元件之間的耦合損耗以及製作成本,更可藉由分波多工技術達到超高速資料傳輸,從多核心處理器到交錯式類比數位轉換器的發展可看出,積體化光電元件於大型積體電路中取代傳統高損耗銅線作為資料傳輸的媒介是未來的發展趨勢。

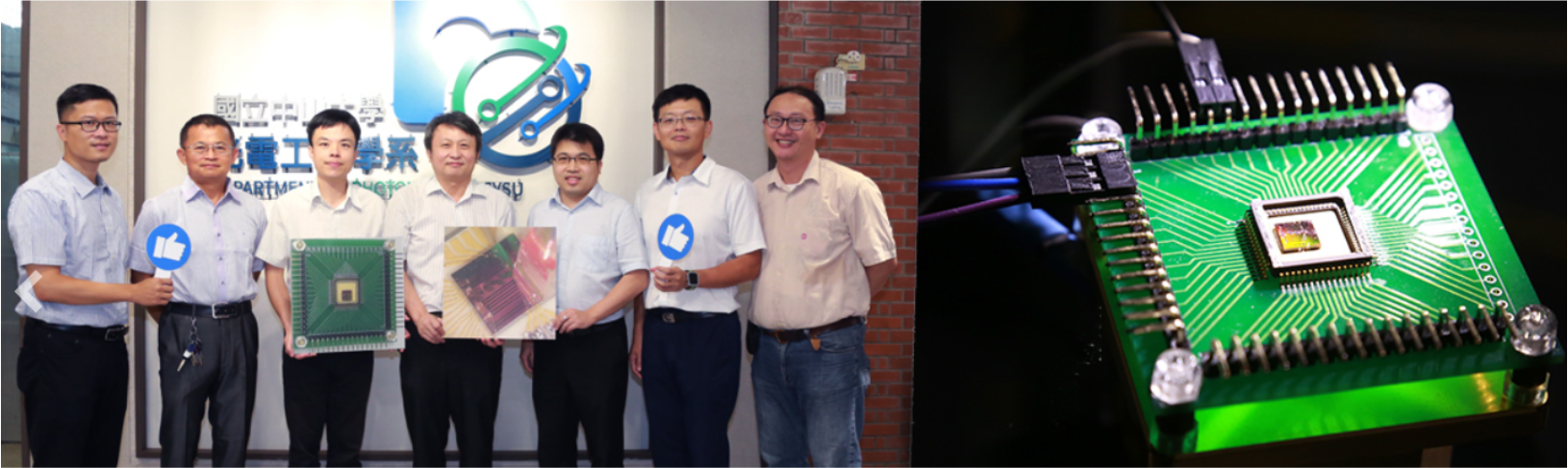

本實驗室擬研發新型光電積體電路架構,嘗試利用標準互補式金屬氧化物半導體(Complementary Metal–Oxide–Semiconductor, CMOS)製程的架構來實現主被動光電元件於超大型積體電路中,設計完成的光電積體電路晶片將委託晶圓廠台積電或聯電代工製作,因為所有光電元件的設計皆遵循標準互補式金屬氧化物半導體製程步驟與考量,因此晶圓廠在製作時甚至不知道他們正在製作光電元件,也因此,目前晶圓廠無法提供任何技術資料與相關PDK用於光電元件的製作。相較於歐美國家晶圓廠Intel與IBM、專為矽晶光子技術建立的OpSiS-IME以及IMEC Multi-Project Wafer Runs甚至於世界領先開發CMOS光電元件的Luxtera Molex,國內在此領域的研究技術處於起步階段。本實驗室將建立整體光積體電路的製程資料庫,此資料庫將可協助晶圓廠建立製作光電積體電路的實力,並向各晶圓廠展示此技術的潛力,以增加其意願進一步最佳化其積體電路架構使其對於光路與電路都有最佳的效能表現,以應付即將到來的光傳輸時代。

實驗室目前以標準CMOS製程為基礎,開發各式光電元件,包含:

- 1. 積體化光波導元件

- 2. 積體化太陽能電池

- 3. 積體化光反射與光濾波元件

- 4. 積體化感測器

- 5. 積體化光隔絕器

此外,實驗室亦將開發相關晶片封裝製程,建立新型全像術曝光系統,並與系上其他教授合作開發新型光電元件。本實驗室最新開發之光柵檢測系統為工商時報所報導